## Use of HSP50216 QPDC for CDMA Applications (IS-95 and CDMA2000)

April 2001

Application Note

Authors: Aaron Algiere and Dejan Radic

AN9928

### Description

This document will explain how to use Intersil's Quad Programmable Down Converter, HSP50216, for CDMA2000 applications. It will provide details on how to combine channels in order to increase the output rate and achieve better filter performance.

## **Configuration 1**

Input Rate: 61.44MSPS (50x)

Output Rate: 2.4576MSPS (2x)

Blocker rejection: > 48dB from 750kHz to 900kHz, > 85dB from 900kHz on

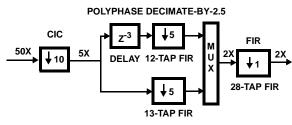

This configuration implements a 1.2288MSPS receiver in the HSP50216 using only one of the four available channels, providing up to four receivers per device. The block diagram of the implementation is shown in Figure 1. It consists of a 5th order CIC decimating by 10 followed by the filter compute engine (FCE) running both a two phase polyphase decimator and a 28-tap FIR.

FIGURE 1. FILTER CONFIGURATION BLOCK DIAGRAM

In general, it is best to perform as much of the decimation as possible in the CIC since this avoids having to use clock cycles to write data to the FCE RAM, but this is limited by the tolerable alias level. The chosen decimation of 10 yields a first alias level of -96.135dB (see HSP50216 data sheet, Table 45 with fS/R = 0.5 / 5 = 0.10). For comparison, a CIC decimation of 25 would give an unacceptable first alias level of -52.269dB (for fS/R = 0.5 / 2 = 0.25).

The flexibility of the HSP50216's FCE is seen in the polyphase and FIR structures of Figure 1. A five-step filter sequence is used to implement it. Step 0 is a wait instruction, which waits for 5 new samples to be transferred from the CIC to the FCE's RAM. When these new samples are available steps 1 and 2 (the 12 and 13-tap FIRs, respectively) are run. The 12-tap FIR is preceded by a 3 sample delay (a read pointer offset) giving its output a total group delay of 3 + (12-1)/2 = 8.5 samples. The 13-tap FIR's group delay, (13-1)/2 = 6, differs by 2.5 samples. Together, these polyphase FIRs generate two equally-spaced output samples for each five new input samples. When multiplexed together, the result is a decimation of 2.5. These outputs are sent to filter sequence step number 3, a 28-tap FIR. Step 4, the final step, is a loop back to step 0's wait for five new input samples. This FCE program, along with the filter coefficient data, is provided in the import filter file.

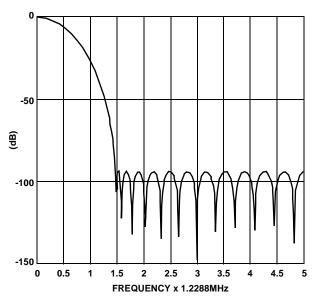

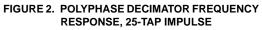

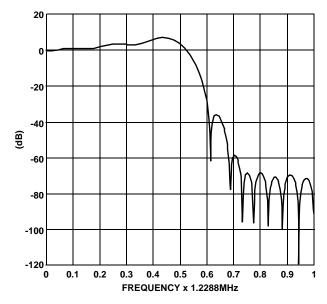

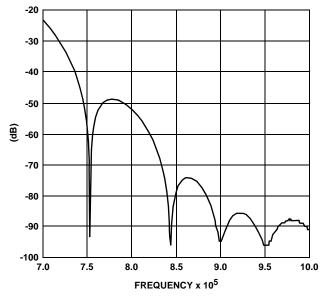

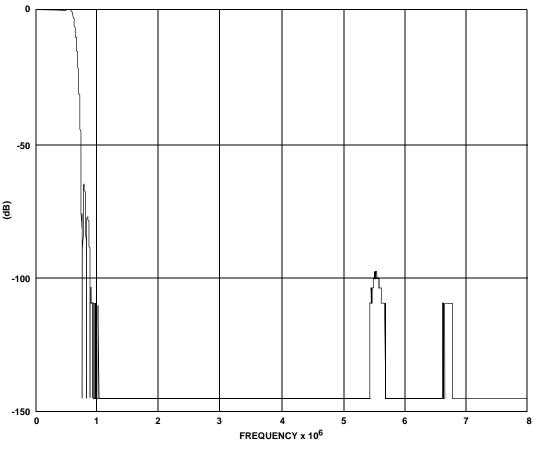

Frequency responses of the polyphase decimator and 28tap FIR are provided in Figures 2 and 3. From Figure 2, the first alias level for decimation by 5 is about -94dB. The loss at high frequencies in the polyphase is compensated for by the gain in the 28-tap FIR (Figure 3).

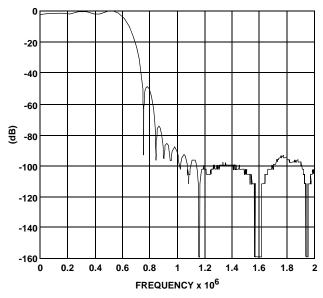

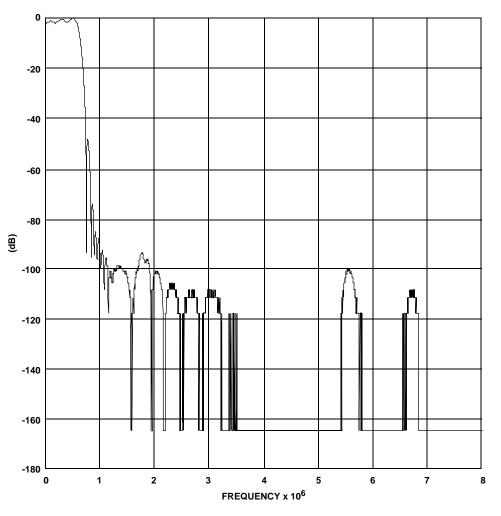

Figures 4, 5, and 6 provide show a complete frequency response of the configuration by doing an actual sweep of the part. The plots used a frequency step of 1kHz and are normalized to a 0dB maximum.

The overall decimation of 50X / 2X = 25 allows 24 bit I and Q data to be available at the serial outputs.

Analysis of computation clock usage:

Available clocks per output = 50 / 2 = 25.

| CLOCKS | FUNCTION                                                                  |

|--------|---------------------------------------------------------------------------|

| 2      | Overhead (Wait, Loop).                                                    |

| 5      | Input Writes from CIC to FCE.                                             |

| 6      | 12-Tap FIR Computation.                                                   |

| 7      | 13-Tap FIR Computation.                                                   |

| 2      | 2 Input Writes to 28-tap FIR.                                             |

| 28     | 2 Runs of 28-Tap FIR (One for Each Polyphase Output) X 14 Clocks Per Run. |

| 50     | Total Clocks to Compute 2 Outputs                                         |

TABLE 1.

All available clocks are used to implement this configuration.

1-888-INTERSIL or 321-724-7143 | Intersil and Design is a trademark of Intersil Americas Inc.

Copyright © Intersil Americas Inc. 2001, All Rights Reserved

1

FIGURE 4. FREQUENCY SWEEP OF THE FILTER AS IMPLEMENTED ON THE HSP50216

FIGURE 3. 28-TAP FIR FREQUENCY RESPONSE

FIGURE 5. FREQUENCY SWEEP ZOOMED IN AROUND 750kHz AND 900kHz BLOCKER FREQUENCIES

## **Configuration 2**

Input Rate: 61.44MSPS (50x)

Output Rate: 2.4576MSPS (2x)

Blocker Rejection: > 65dB from 750kHz to 900kHz, > 103dB from 900kHz On

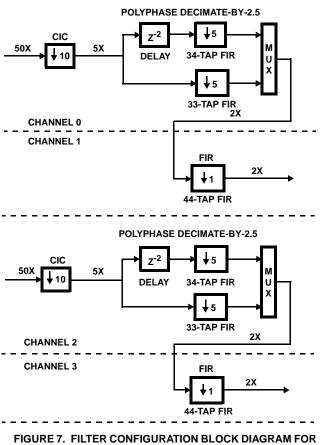

This configuration implements a 1.2288MSPS receiver in the HSP50216 using two of the four available channels, providing up to two receivers per device. The block diagram of the implementation of two receivers is shown in Figure 7 below. It consists of, in the first channel, a 5th order CIC decimating by 10 followed by the filter compute engine (FCE) running a two-phase polyphase decimator and, in the second channel, a 44-tap FIR.

TWO RECEIVERS

As shown in the first configuration, the chosen decimation of 10 in this configuration with a 50X input yields a first alias level of -96.135dB.

The decimate-by-2.5 filter is implemented in the FCE as a 4-step sequence. Step 0 is a wait instruction, which waits for 5 new samples to be transferred from the CIC to the FCE's RAM. When these new samples are available steps 1 and 2 (the 34 and 33-tap FIRs, respectively) are run. The 34-tap FIR is proceeded by a 2 sample delay (a read pointer offset) giving its output a total group delay of 2 + (34-1)/2 = 18.5samples. The 33-tap FIR's group delay, (33-1)/2 = 16, differs by 2.5 samples. Together, these polyphase FIRs generate two equally-spaced output samples for each five new input samples. When multiplexed together, the result is a decimation of 2.5. These outputs are sent to the FCE of the next channel, which runs a 44-tap FIR. Step 3, the final step of the polyphase sequence, is a loop back to step 0's wait for five new input samples. This FCE program, along with the polyphase filter coefficient data, is provided in the import filter file.

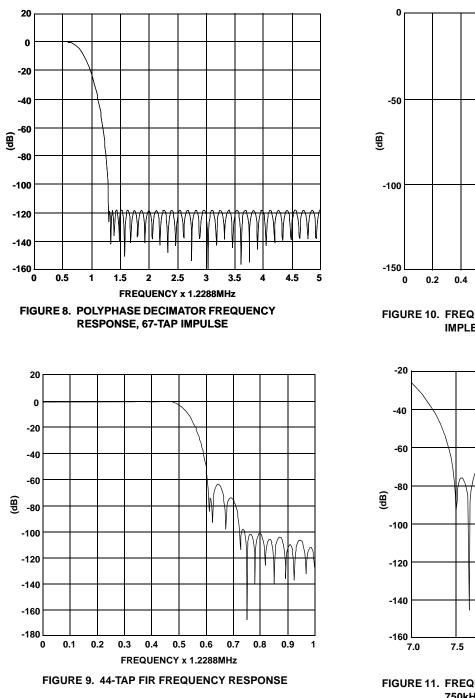

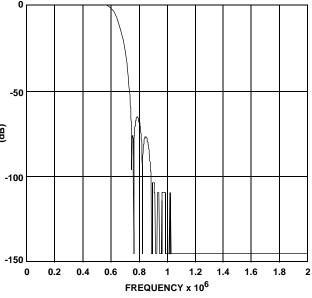

Frequency responses of the polyphase decimator and 44-tap FIR are provided in Figures 8 and 9. From Figure 8, the first alias level in the signal bandwidth for decimation by 5 is about -120dB.

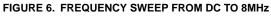

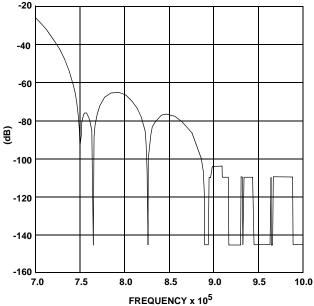

Figures 10, 11, and 12 provide show a complete frequency response of the configuration by doing an actual sweep of the part. The plots used a frequency step of 1kHz and are normalized to a 0dB maximum.

The overall decimation of 50X / 2X = 25 allows 24 bit I and Q data to be available at the serial outputs.

## Analysis of Computation Clock Usage

#### Channel 0

Available clocks per output = 50 / 2 = 25

| CLOCKS | FUNCTION                          |

|--------|-----------------------------------|

| 2      | Overhead (Wait, Loop)             |

| 5      | Input Writes from CIC to FCE      |

| 17     | 34-Tap FIR Computation            |

| 17     | 33-Tap FIR Computation            |

| 41     | Total Clocks to Compute 2 Outputs |

Channel 0 has 50 clocks available to produce 2 outputs (25 clocks per output), but its configuration uses only 41. These available 9 clock cycles permit up to an additional 18 taps to be added to channel 0's filtering if desired.

#### Channel 1

Available clocks per output = 25 (same as channel 0)

| CLOCKS | FUNCTION                                             |

|--------|------------------------------------------------------|

| 2      | Overhead (Wait, Loop)                                |

| 2      | Input Writes from Channel 0's FCE to Channel 1's FCE |

| 44     | 2 Runs of the 44-Tap Filter x 22 Clocks Per Run      |

| 48     | Total Clocks to Compute 2 Outputs                    |

Channel 1's configuration uses 48 of its available 50 clocks in computing two output samples. An additional 4 taps could be added to this filter if desired.

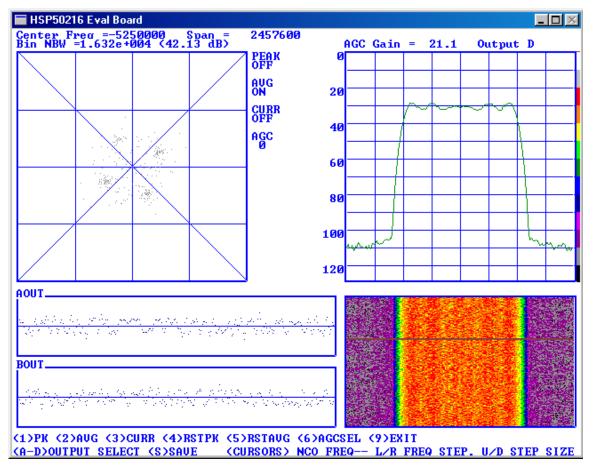

FIGURE 10. FREQUENCY SWEEP OF THE FILTER AS IMPLEMENTED ON THE HSP50216

FIGURE 11. FREQUENCY SWEEP ZOOMED IN AROUND 750kHz AND 900kHz BLOCKER FREQUENCIES

FIGURE 12. FREQUENCY SWEEP TO 8MHz

# Use of HSP50216 EVAL Software for this Application

The eval board software is the perfect tool to evaluate performance of the part, configure registers, verify filter designs, and display the I/Q constellation and spectrum of the output. Connectivity to the eval board is supported only by Windows 95 and 98, however Windows NT and 2000 may be used for generating the register value files which may be downloaded to the chip with the user's own hardware.

NOTE: The software can configure the register value files even if the HSP50216/ ISL5216 Evaluation Board is not connected.

The configuration file is loaded by selecting option 8 in the main menu of the software. Enter only the root name of the configuration, where the root name is the file name preceding the .0, .1, .2, .3 and .top file extensions.

Figure 14 shows the channel 0 data path settings for Configuration 1 (in the configuration files for this example, channels 1, 2 and 3 are configured the same as channel 0). It shows the 61.44MSPS input rate, 5th order CIC decimation of 10, and an NCO center frequency as well as the source input bus. The imported filter program specified in

6

options 13, 27 and 28 contains both the FCE program and 12, 13 and 28-tap FIR coefficients (see Figure 1). Imported filters are hand-coded filter programs which bypass the software's automatic register value generation.

When loading of the configuration is completed (main menu option 8), initialize the eval board using option 17, compute the register value files using option 10, and download the register values to the '216 using option 12. Finally, select run and display (option 13) to see the '216 output in real time.

As noted previously, if only register values are needed, option 10 in the Main Menu will compute register values for each of the channels, and store them in the files file\_name.r0, file\_name.r1, file\_name.r2, file\_name.r3 and file\_name.rtp where file\_name is name entered into the load or save configuration options (8 and 9) from the main menu. These files are human readable text files containing register numbers and values in hex.

| HSP50216 Eval Board console                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auto 💽 🛄 🖻 🔂 🖆 🗛                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| HSP50216 CONFIGURATION SOFTWARE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Channel 3 Data Path   File Name ic2k6144   INPUT FILTERING   12) Sample Rate 61440000 Hz   (13) Sample Rate 61440000 Hz   (2) Input Source RIM (21) Filter Program   (3) Input Source RIM (22) Filter Program   (4) FX4 Point Casted   (5) Input Mode Gated (28) Decimation   (5) Provenux Delay 0 Orante RMO   (3) Center Preq. +4000000 Hz   (4)  0   (3) Center Preq. +4000000 Hz   (4)  0   (5) Center Preq.  0   (6) PH Dist Preq.  0   (11) CIC Order 5 (12) Decimation   (12) Decimation 10   (0) Main Menu |

| ENTER SELECTION:<br>(C) Intersil Corp 2001 Version 1.01a                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

FIGURE 13. EVAL BOARD SOFTWARE MAIN MENU

| 🔀 HSP50216 Eval Board console 📃 🗖                        |  |

|----------------------------------------------------------|--|

| Auto 💽 🗈 🛍 🔂 🖆 🗛                                         |  |

| HSP50216 CONFIGURATION SOFTWARE                          |  |

| Channel 3 Data Path<br>File Name                         |  |

| ENTER SELECTION:<br>(C) Intersil Corp 2001 Version 1.01a |  |

FIGURE 14. EVAL BOARD SOFTWARE DATA PATH MENU

#### FIGURE 15. SCREEN SHOT FROM HSP50216 EVALUATION BOARD SOFTWARE

All Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems.

Intersil Corporation's quality certifications can be viewed at website www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site www.intersil.com